Debouncer v2

I wrote a quick debouncer code in VHDL that I thought people could enjoy and may be useful for FPGA projects. For more info on debouncers see this post.

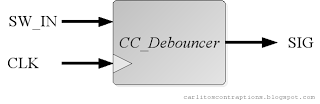

As shown in the block diagram below, it takes as inputs a switch signal (SW_IN) and a clock signal (CLK) and outputs a signal SIG.

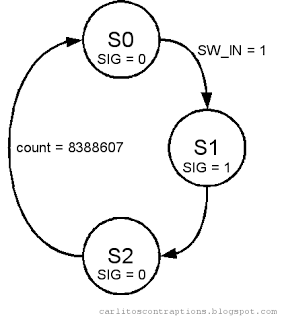

When SW_IN goes high, the module outputs a once-clock-cycle wide pulse on the next clock rising edge. Then it waits for 8388607 clock cycles (~ 0.17 s when clocked @ 50MHz). This is illustrated in the state transition diagram below.

When SW_IN goes high, the module outputs a once-clock-cycle wide pulse on the next clock rising edge. Then it waits for 8388607 clock cycles (~ 0.17 s when clocked @ 50MHz). This is illustrated in the state transition diagram below.

You can download the code here.

You can download the code here.